EMV-Prüfung: Zuverlässige Elektronik entwickeln in 7 Schritten

Klaus Kuboth

27.11.2025

Ein praxisnaher Leitfaden für robuste und EMV-sichere Elektronik

Eine starke elektromagnetische Verträglichkeit (EMV) ist das A und O zuverlässiger Elektronik. Nur so funktionieren Systeme störungsfrei, ohne andere Geräte zu beeinflussen oder selbst gestört zu werden. Doch kompakte Designs und hohe Datenraten machen das zunehmend schwieriger. In diesem Beitrag erfahren Sie, wie Sie in sieben Schritten eine solide Grundlage für EMV-freundliches Design schaffen.

EMV-Prüfung & EMC Testing: Warum Strategie entscheidend ist

Für eine zuverlässige EMV genügt es nicht, am Ende des Projekts einfach nur einen Knopf zu drücken. Es braucht einen strategischen, iterativen Ansatz, der Bestandteil jedes einzelnen Entwicklungsschritts ist. Das fängt schon bei der Leiterplatte an, wo hochfrequente Ströme und kritische Wechselwirkungen entstehen. Der nachfolgende 7-schrittige Prozess hilft Ihnen dabei, verborgene EMV-Risiken frühzeitig zu erkennen, Compliance sicherzustellen und ein robustes, störungsfreies Produkt zu entwickeln.

Schritt 1: ECAD-Check für EMV-konformes Design

Ihre Simulation ist nur so gut wie Ihre Daten. Wenn Sie Routing-Details oder Layout-Artefakte in der Leiterplatte übersehen, bleiben EMV-Probleme leicht unbemerkt. Werden sie dann erst in einer späteren Testphase entdeckt, sind Korrekturen in der Regel weitaus kostspieliger. Ein präzises digitales Modell hilft Ihnen dabei, alle „realen“ Stolperfallen frühzeitig in der Analyse zu erfassen.

Importieren Sie Ihre ECAD-Dateien in Ansys SIwave, um die Leiterplatte originalgetreu abzubilden. Das Tool nutzt 2,5D-Löser, um die Signal- und Versorgungsintegrität (SI/PI) zu analysieren und anfängliche Problembereiche wie Impedanzfehlanpassungen, Spannungsabfälle oder Ground-Bounce-Bereiche zu identifizieren. Sie erkennen schnell, wo das Design möglicherweise gegen EMV-Richtlinien verstößt, und legen die Grundlagen für die nachfolgende Untersuchung.

Whitepaper: Elektronikkomponenten zuverlässig gestalten

Erfahren Sie, wie frühe EMV-Simulation Zuverlässigkeit und Sicherheit erhöht.

Jetzt Whitepaper zur EMV-Simulation lesen

Schritt 2: Ursachenanalyse für EMV-Probleme

Haben Sie die ersten „Hotspots“ identifiziert, sollten Sie sich genauer ansehen, warum diese Probleme auftreten. Gibt es unerwünschte Resonanzen? Entstehen zu starke Kopplungseffekte zwischen Leiterbahnen? Treten Signalreflexionen durch eine schlechte Impedanzanpassung auf? Sobald Sie diese spezifischen Ursachen herausgefunden haben, können Sie gezielte Maßnahmen ergreifen.

Mithilfe von Frequenzsweeps und S-Parameter-Analysen können Sie in Ansys SIwave Resonanzen identifizieren, Kopplungspfade analysieren und die Feldverteilung visualisieren. Die Diagnostik-Tools zeigen Ihnen, welche physikalischen Strukturen das Problem verursachen – etwa Versorgungsebenen, Leiterbahnen oder Durchkontaktierungen.

Schritt 3: Layoutänderung und Bauteilanpassung: Risiken ausräumen

EMV ist keinesfalls die Kirsche auf der Sahnetorte, sondern muss von Anfang an mitgedacht werden. Je früher Sie Layout, Bestückung und Entkopplung entsprechend den identifizierten Problemquellen optimieren, desto robuster und kosteneffizienter wird Ihr Produkt. Die Ursachen an der Wurzel zu packen kann bedeuten, kritische Leiterbahnen umzuverlegen, Komponenten umzuplatzieren, Stacks zu optimieren, Splitplanes zu beseitigen oder Entkopplungsstrategien zu verstärken.

Passen Sie das Layout im ECAD-Tool an und aktualisieren Sie anschließend das Ansys SIwave-Modell. „Was-wäre-wenn“-Iterationen helfen Ihnen dabei, herauszufinden, wie sich Routing-Modifikationen, Stackup-Revisionen oder neue Erdungs- bzw. Entkopplungsmaßnahmen auf das System auswirken – und das ohne einen langen Trial-and-Error-Zyklus.

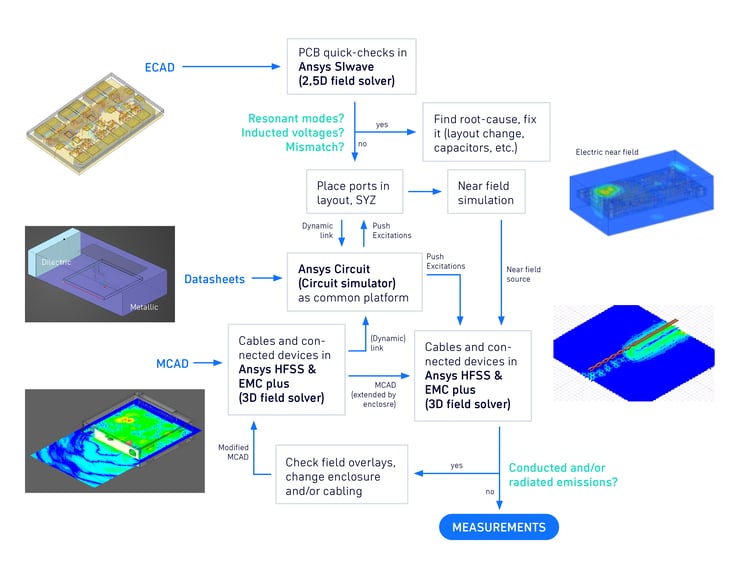

EMV-Workflow in 7 Schritten | © CADFEM Germany GmbH

Schritt 4: Schaltungsanalyse für zuverlässige EMV-Compliance

In der Praxis treten EMV-Probleme häufig an der Schnittstelle zwischen Layout und Schaltungsdynamik auf. Dabei spielen sowohl bewusste Designentscheidungen als auch parasitäre Effekte eine Rolle. Verschaffen Sie sich eine echte Systemperspektive, indem Sie die Simulation auf der PCB-Ebene mit einer vollständigen Schaltungssimulation kombinieren.

Exportieren Sie das Übertragungsverhalten wichtiger Leiterbahnen aus Ansys SIwave und koppeln Sie diese Informationen anschließend mit einer systemweiten Schaltungssimulation in Ansys AEDT Circuit. Die genauen Signalwellenformen dienen als wichtige Datengrundlage für nachfolgende Analysen der Störfelder. So erhalten Sie Einblicke in das dynamische Verhalten der Schaltungen und die Auswirkungen parasitärer Effekte auf die Systemperformance.

Schritt 5: Nah- und Fernfeldsimulation: Verborgene Risiken aufdecken

Sobald Sie das Verhalten Ihrer Schaltung verstanden haben, sollten Sie herausfinden, wie viel elektromagnetische Energie abgestrahlt wird. Ziel ist es, mithilfe von Nah- und Fernfeldanalysen gezielt Schwachstellen im Design zu erkennen. So können Sie frühzeitig Problembereiche identifizieren, die abgeschirmt, besser geerdet oder layouttechnisch angepasst werden müssen.

Nutzen Sie dazu die in Ansys AEDT Circuit simulierten Signalwellenformen und importieren Sie diese zurück in Ansys SIwave. Dort können Sie präzise berechnen, an welchen Punkten und mit welcher Stärke störende Felder rund um die Leiterplatte oder in definierten Abständen auftreten. Die Visualisierung macht Hotspots sichtbar, die zu Compliance-Problemen oder plötzlichen Störungen führen können.

Schritt 6: 3D-Vollwellensimulation: Die Realität abbilden

Zur realitätsnahen EMV-Bewertung muss man berücksichtigen, dass alle Komponenten – Leiterplatte, Kabel, Stecker, Gehäuse – zusammenwirken. Darauf sollten Sie sich als nächstes konzentrieren: Untersuchen Sie das Verhalten des Geräts in seiner Betriebsumgebung. Also nicht nur die Leiterplatte, sondern das System als Ganzes. Diese umfassende Simulation identifiziert mögliche EMV-Fehlerquellen und gibt Hinweise auf Wechselwirkungen im realen Betriebsumfeld.

Verwenden Sie die von Ansys SIwave berechneten Nahfelder als Quellen in einer 3D-Vollwellensimulation mit Ansys HFSS oder Ansys EMC Plus . Die Tools modellieren das Verhalten Ihres Systems unter Testbedingungen. Dabei werden auftretende Kopplungen und Feldab- und -einstrahlungen ermittelt. So finden Sie Bereiche, in denen Abschirmungsmaßnahmen notwendig sind oder die Bauteilplatzierung angepasst werden sollte.

Schritt 7: EMV-Messung und Validierung für Compliance

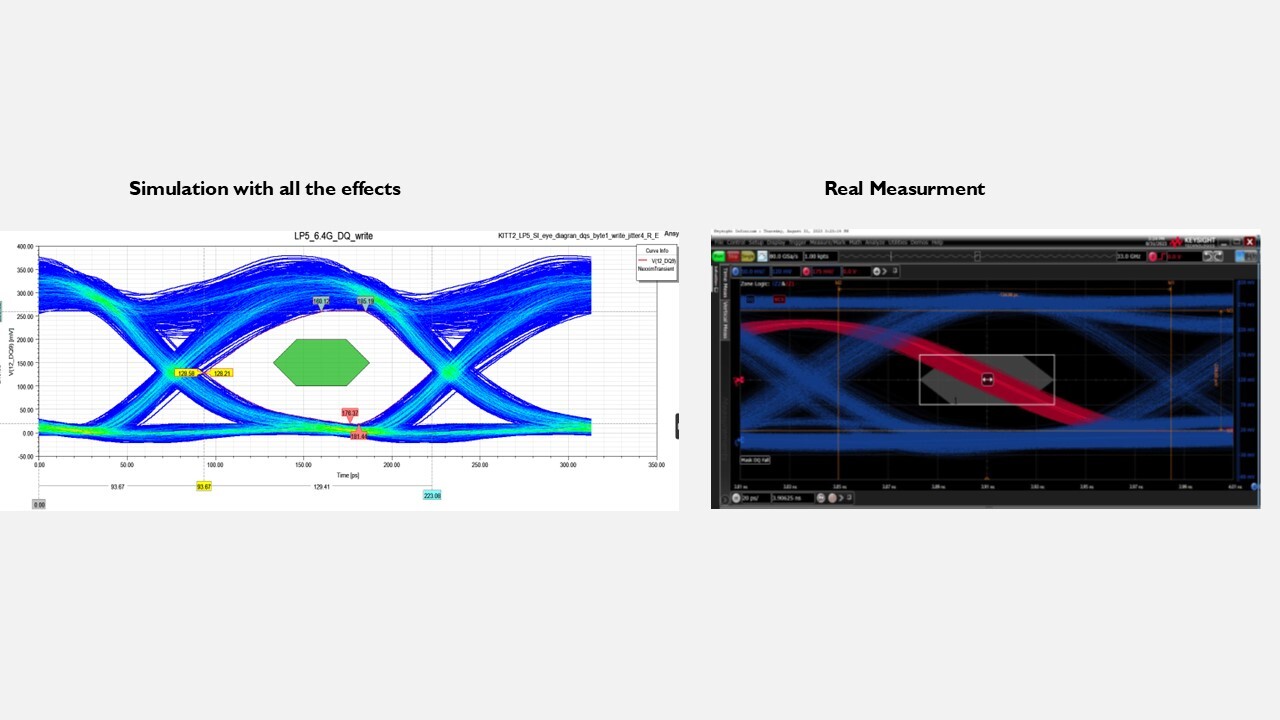

Wenn Sie Ihre Simulation mit physikalischen Messungen validieren müssen, ist jetzt der richtige Zeitpunkt dafür. Gleichen Sie digitale Vorhersagen mit physikalischen Compliance-Messungen ab, um sicherzustellen, dass Ihr Workflow auf dem richtigen Weg ist. So sehen Sie auch gleich, wo noch Verbesserungsbedarf besteht.

Integrieren Sie den Messaufbau in das Ansys 3D-Modell. Sobald Labordaten verfügbar sind, überlagern Sie diese Ergebnisse mit Ihren Simulationen. Falls nötig, kalibrieren Sie Materialeigenschaften neu oder passen Sie Modellannahmen an. Diesen Prozess können Sie nutzen, um die Simulationsgenauigkeit für zukünftige Projekte zu verbessern – und der Aufwand für den Messaufbau macht sich im Nu bezahlt.

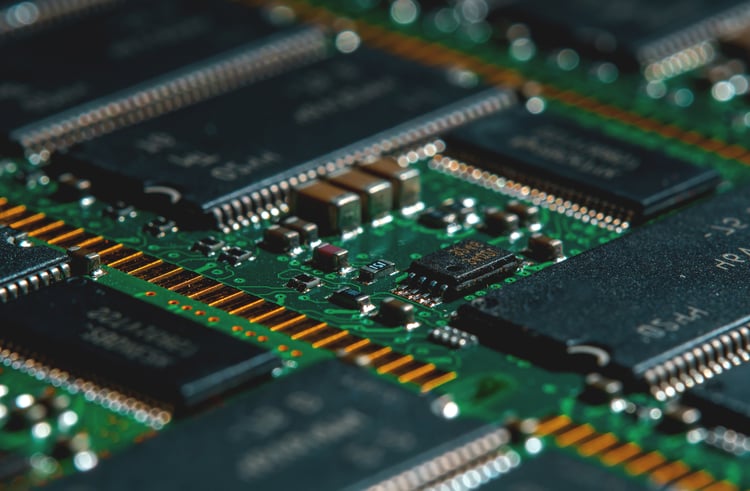

Elektronische Leiterplattenkomponente | © Adobe Stock/CADFEM Germany GmbH

Fazit: EMV-Prüfung & EMC Testing als Schlüssel zur Zuverlässigkeit

Bei der EMV-Simulation geht es nicht nur um Technologie. Es geht darum, Zuverlässigkeit und Compliance in Ihren gesamten Entwicklungsprozess zu integrieren, angefangen bei der Leiterplatte. Mit diesem strukturierten Workflow und den richtigen Tools für jede Phase verwandeln Sie komplexe EMV-Herausforderungen in Chancen – für eine intelligentere, schnellere und besser planbare Produktentwicklung. Wenn Elektronik immer kleiner und Designzyklen immer kürzer werden, verschafft Ihnen dieser proaktive Ansatz einen entscheidenden Wettbewerbsvorteil. Erfahren Sie in unserem Whitepaper, wie frühzeitige EMV-Simulation hilft, kostspielige Fehlfunktionen und Verzögerungen in späteren Entwicklungsphasen zu vermeiden.